IBM和三星声称他们已经在半导体设计方面取得了突破。在旧金山举行的IEDM会议的第一天,这两家公司公布了一种在芯片上垂直堆叠晶体管的新设计。在目前的处理器和SoC中,晶体管平放在硅的表面,然后电流从一侧流向另一侧。相比之下,垂直传输场效应晶体管(VTFET)彼此垂直放置,电流垂直流动。

根据IBM和 三星 的说法,这种设计有两个优点。首先,它将使他们能够绕过许多性能限制,使摩尔定律超越IBM目前的纳米片技术。更重要的是,由于更大的电流流动,这种设计导致了更少的能量浪费。他们估计,VTFET将使处理器的速度比使用FinFET晶体管设计的芯片快一倍,或减少85%的功率。IBM和三星声称,该工艺有朝一日可能允许 手机 在一次充电的情况下使用一整个星期。他们说,这也可以使某些能源密集型的任务,包括加密工作,更加省电,从而减少对环境的影响。

IBM和三星还没有说他们计划何时将该设计商业化。他们并不是唯一试图超越1纳米障碍的公司。今年7月, 英特尔 表示,它的目标是在2024年之前最终完成亚微米级芯片的设计。该公司计划利用其新的"英特尔20A"节点和RibbonFET晶体管完成这一壮举。

在外媒报道刊出后,IBM随后澄清,VTFET将帮助它扩展到其现有的芯片技术之外,而不一定精选与扩展制程到1纳米以下,同时公司还指出,性能或电池寿命方面可以看到长足进步,但如果要同时进行则会有难度。

【来源:cnBeta.COM】

广期所计划推出咖啡期货 透

广期所计划推出咖啡期货 透

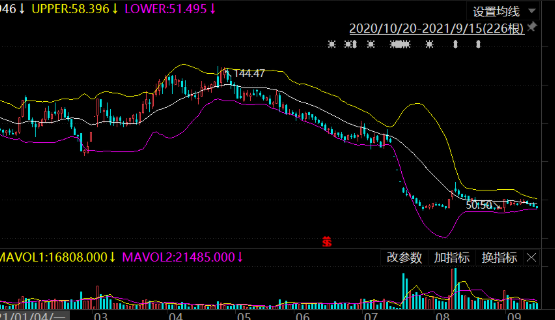

A股市场风格高速切换 中小

A股市场风格高速切换 中小

江特电机一字跌停 因涉嫌信

江特电机一字跌停 因涉嫌信

北京多家景区不断完善票务服

北京多家景区不断完善票务服

美国失业人数创新低 美联储

美国失业人数创新低 美联储

杭州众祺4S店买高配车型变低

杭州众祺4S店买高配车型变低

福建石狮帮助中小型食品生产

福建石狮帮助中小型食品生产

Grab上市首日大跌 股价在一

Grab上市首日大跌 股价在一

48小时点击排行

48小时点击排行