在加州旧金山举办的 IEDM 2021 国际电子元件会议中,IBM 与三星共同公布了名为垂直传输场效应晶体管 (VTFET) 的芯片设计技术,该技术将晶体管以垂直方式堆叠,并且让电流也改以垂直方式流通,借此让晶体管数量密度再次提高之外,更大幅提高电源使用效率,并且突破目前在 1nm 制程设计面临瓶颈。

相较传统将晶体管以水平方式堆叠的设计,垂直传输场效应晶体管将能增加晶体管数量堆叠密度,并且让运算速度提升两倍,同时通过让电流以垂直方式流通,也让电力损耗降低 85%(性能和续航不能同时兼顾)。

IBM 和三星声称,该工艺有朝一日可能允许手机在一次充电的情况下使用一整个星期。他们说,这也可以使某些能源密集型的任务,包括加密工作,更加省电,从而减少对环境的影响。

据了解到,目前 IBM 与三星尚未透露预计何时将垂直传输场效应晶体管设计应用在实际产品,但预期很快就会有进一步消息。

不过,台积电已经在今年 5 月宣布与中国台湾大学、麻省理工学院共同研究,通过铋金属特性突破 1nm 制程生产极限,让制程技术下探至 1nm 以下。而英特尔日前也已经公布其未来制程技术发展布局,除了现有纳米 (nm) 等级制程设计,接下来也会开始布局埃米 ( ) 等级制程技术,预计最快会在 2024 年进入 20A 制程技术。

【来源:IT之家】【作者:远洋】

广期所计划推出咖啡期货 透

广期所计划推出咖啡期货 透

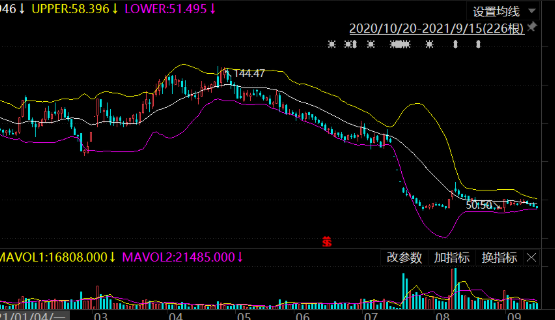

A股市场风格高速切换 中小

A股市场风格高速切换 中小

江特电机一字跌停 因涉嫌信

江特电机一字跌停 因涉嫌信

北京多家景区不断完善票务服

北京多家景区不断完善票务服

美国失业人数创新低 美联储

美国失业人数创新低 美联储

杭州众祺4S店买高配车型变低

杭州众祺4S店买高配车型变低

福建石狮帮助中小型食品生产

福建石狮帮助中小型食品生产

Grab上市首日大跌 股价在一

Grab上市首日大跌 股价在一

48小时点击排行

48小时点击排行